# Low temperature atomic layer deposited ZnO photo thin film transistors

Feyza B. Oruc, Levent E. Aygun, Inci Donmez, Necmi Biyikli, Ali K. Okyay, and Hyun Yong Yu

Citation: Journal of Vacuum Science & Technology A 33, 01A105 (2015); doi: 10.1116/1.4892939

View online: http://dx.doi.org/10.1116/1.4892939

View Table of Contents: http://scitation.aip.org/content/avs/journal/jvsta/33/1?ver=pdfcov Published by the AVS: Science & Technology of Materials, Interfaces, and Processing

# Articles you may be interested in

Effect of Al concentration on Al-doped ZnO channels fabricated by atomic-layer deposition for top-gate oxide thin-film transistor applications

J. Vac. Sci. Technol. B 32, 041202 (2014); 10.1116/1.4880823

Schottky barrier source-gated ZnO thin film transistors by low temperature atomic layer deposition Appl. Phys. Lett. **103**, 253503 (2013); 10.1063/1.4836955

Electrical conductivity and photoresistance of atomic layer deposited Al-doped ZnO films J. Vac. Sci. Technol. A **31**, 01A146 (2013); 10.1116/1.4772665

Low temperature atomic layer deposited Al-doped ZnO thin films and associated semiconducting properties J. Vac. Sci. Technol. B **30**, 031210 (2012); 10.1116/1.4710519

High performance thin film transistor with low temperature atomic layer deposition nitrogen-doped ZnO Appl. Phys. Lett. **91**, 183517 (2007); 10.1063/1.2803219

# Low temperature atomic layer deposited ZnO photo thin film transistors

Feyza B. Oruc, Levent E. Aygun, Inci Donmez, Necmi Biyikli, and Ali K. Okyay<sup>a)</sup>

Institute of Materials Science and Nanotechnology, Bilkent University, Bilkent, 06800 Ankara, Turkey;

UNAM—National Nanotechnology Research Center, Bilkent University, Bilkent, 06800 Ankara, Turkey;

and Department of Electrical and Electronics Engineering, Bilkent University, Bilkent, 06800 Ankara, Turkey

Hyun Yong Yu

The School of Electrical Engineering, Korea University, Seoul 136-701, South Korea

(Received 27 May 2014; accepted 1 August 2014; published 20 August 2014)

ZnO thin film transistors (TFTs) are fabricated on Si substrates using atomic layer deposition technique. The growth temperature of ZnO channel layers are selected as 80, 100, 120, 130, and 250 °C. Material characteristics of ZnO films are examined using x-ray photoelectron spectroscopy and x-ray diffraction methods. Stoichiometry analyses showed that the amount of both oxygen vacancies and interstitial zinc decrease with decreasing growth temperature. Electrical characteristics improve with decreasing growth temperature. Best results are obtained with ZnO channels deposited at 80 °C;  $I_{on}/I_{off}$  ratio is extracted as  $7.8 \times 10^9$  and subthreshold slope is extracted as 0.116 V/dec. Flexible ZnO TFT devices are also fabricated using films grown at 80 °C.  $I_{D}$ – $V_{GS}$  characterization results showed that devices fabricated on different substrates (Si and polyethylene terephthalate) show similar electrical characteristics. Sub-bandgap photo sensing properties of ZnO based TFTs are investigated; it is shown that visible light absorption of ZnO based TFTs can be actively controlled by external gate bias. © 2014 American Vacuum Society. [http://dx.doi.org/10.1116/1.4892939]

#### I. INTRODUCTION

ZnO has been gaining significant inertia as a promising material for transparent electronics applications. ZnO is quickly replacing amorphous silicon (a-Si) based thin film transistor (TFT) technology for flat panel displays, thanks to its outstanding electrical and optical properties. 1-3 ZnO is a wide bandgap  $(E_g \sim 3.37 \text{ eV})$ , n-type semiconductor, and it has a natural tendency to form good quality polycrystalline films even deposited at room temperature. <sup>4</sup> ZnO TFTs exhibit higher electron mobility compared to traditional a-Si counterparts. ZnO is also compatible with inexpensive flexible substrates such as plastics owing to low synthesis temperatures.<sup>5,6</sup> Due to its wide bandgap, ZnO is transparent in the visible range, a trait not shared by a-Si. ZnO has low light sensitivity that is desired for electronic active matrix of flat panel displays. Moreover, visible photo-response of ZnO TFTs is shown to be actively tunable using an external actuation. There is a significantly vibrant literature on ZnO channel TFTs deposited with different methods such as physical vapor deposition, chemical vapor deposition, chemical solution deposition, molecular beam epitaxy, and atomic layer deposition (ALD). 1-4,9-12 The on-to-off current ratios,  $I_{on}/I_{off}$ , of these devices range from 10 to  $10^8$  with reported electron mobility values between 0.031 and 56.43 cm<sup>2</sup>/V-s.<sup>2,13-17</sup> Among all these techniques, ALD is promising due to the low growth temperature, large area uniformity, precise thickness control, highly conformal deposition, and scalability to roll-to-roll processes. Low temperature processing is very crucial for compatibility with flexible substrates.

In this paper, we present electrical and optical properties of low-temperature ALD grown ZnO and analyze the effect of channel layer growth temperature on the electrical characteristics of bottom-gate ZnO TFTs. We also investigate the optical properties of ZnO TFTs and show that ZnO has response to visible light, which can be tuned with applied electrical gate voltage. Due to this significant property, ZnO thin films may be used in novel applications like smart glasses.

# II. EXPERIMENT

#### A. Materials characterization

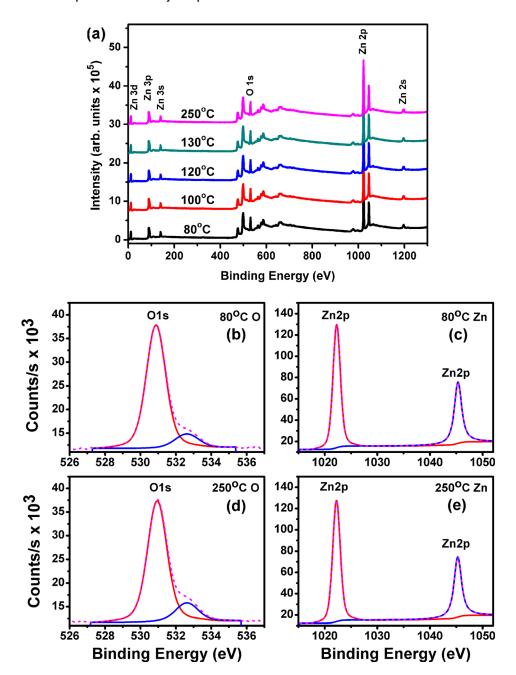

Crystal defects such as oxygen vacancies and interstitial zinc are claimed to be responsible for the effective n-type behavior in unintentionally doped ZnO films. Although there is still debate on the exact mechanisms of defects' contribution to charge carrier concentration, it was shown that low carrier concentrations are achieved with better stoichiometry. In this work, the surface chemical compositions of the ALD-grown ZnO films are extracted by x-ray photoelectron spectroscopy measurements (XPS-Thermo K-Alpha monochromated high-performance XPS spectrometer). Figure 1(a) shows the survey scan results of ZnO films grown at different temperatures. Film stoichiometry was determined based on the ratios of the areas under the peaks in measured survey scan data (see Table I). As the growth temperature decreases, films become more stoichiometric. In other words, the amount of both oxygen vacancies and interstitial zinc decrease with decreasing growth temperature. The O 1s spectrum of films deposited at 80 and 250 °C are fitted by two subpeaks, which belong to O-Zn and O-H bonding states [see Fig. 1(b)]. The ratio of areas under these subpeaks is used to extract O-H/O-Zn ratio for each growth temperature. At 80 °C, O-H/O-Zn ratio is extracted as 0.17; however, at 250 °C, this ratio decreases down to 0.12. Zn 2p spectrum confirms the existence of Zn-O bonding states and proves that Zn atoms bind only to O atoms in this process.

<sup>&</sup>lt;sup>a)</sup>Electronic mail: aokyay@ee.bilkent.edu.tr

Fig. 1. (Color online) (a) XPS survey scan spectra of ZnO films, (b)–(e) model fit for high resolution XPS scans of films deposited at  $80 \,^{\circ}$ C [(b) and (c)] and  $250 \,^{\circ}$ C [(d) and (e)]. Dashed curves represent the total measured signal, and the solid curves are O–Zn, O–H, and Zn–O model fit curves.

Table I. Stoichiometry analyses of ALD grown ZnO films deposited at various temperatures.

|                         | Atomic percentage ratio (%) |       |       |  |

|-------------------------|-----------------------------|-------|-------|--|

| Growth temperature (°C) | Oxygen                      | Zinc  | O/Zn  |  |

| 80                      | 49.88                       | 50.12 | 0.995 |  |

| 100                     | 49.85                       | 50.15 | 0.994 |  |

| 120                     | 48.05                       | 51.95 | 0.924 |  |

| 130                     | 48.57                       | 51.43 | 0.944 |  |

| 250                     | 48.31                       | 51.69 | 0.934 |  |

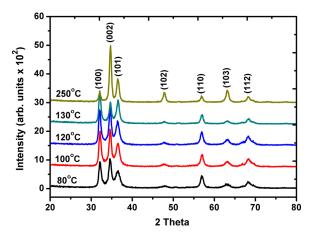

X-ray diffraction (XRD—Panalytical X'pert Pro MRD) measurements indicated that ALD grown ZnO films possess a hexagonal wurtzite crystal structure with no preferred orientation at lower temperature values. However, at 250 °C, the intensity of (002) orientation increases dramatically. The diffraction maxima occurred at (100), (002), and (101) crystallographic orientations for all ZnO films (see Fig. 2). XRD results support the natural tendency of ZnO to form good quality polycrystalline films even at temperatures lower than 100 °C.

#### B. Device fabrication

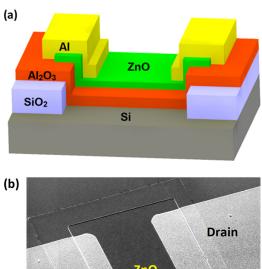

TFT fabrication process starts with the deposition of 210-nm-thick SiO<sub>2</sub> layer on top of chemically cleaned, highly

Fig. 2. (Color online) XRD patterns of ZnO films grown at different temperatures.

doped (10–18 m $\Omega$ -cm) p-type (111) Si wafer with a plasma enhanced chemical vapor deposition system. Active device areas are created by a photolithography process followed by wet etching of SiO<sub>2</sub> layer using a buffered oxide etch solution (NH<sub>4</sub>–HF, 7:1). Highly doped Si wafer is used as the back-gate electrode. Twenty-nanometer-thick Al<sub>2</sub>O<sub>3</sub> and 10-nm-thick ZnO layers are both deposited in a Cambridge Nanotech Inc., Savannah S100 ALD system. The growth temperature of Al<sub>2</sub>O<sub>3</sub> layer is 250 °C. ZnO channel layer deposition temperatures are 80, 100, 120, 130, and 250 °C. The precursors for zinc and oxygen are diethylzinc (DEZn) and milli-Q water (H<sub>2</sub>O), respectively. The processing cycle consists of 15 ms DEZn pulse and 15 ms H<sub>2</sub>O pulse, purging times are adjusted according to the growth temperature. ZnO channels are patterned by wet etching in diluted H<sub>2</sub>SO<sub>4</sub>

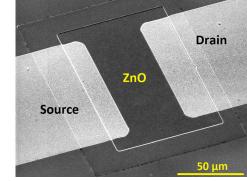

Fig. 3. (Color online) (a) Schematic view of device structure and (b) scanning electron microscope image of a ZnO TFT.

solution. 80-nm-thick Al layer is deposited for electrical contact pads (see Fig. 3).

Fabrication of flexible ZnO TFTs starts with 50 nm Al deposition on polyethylene terephthalate (PET) substrates with thermal evaporator and patterned by commercial Al etchant to create gate contact electrodes. Twenty nanometers thick  $Al_2O_3$  and 14 nm thick ZnO layers are grown at  $80\,^{\circ}\text{C}$  using the thermal-ALD system. ZnO layer is patterned by a diluted  $H_2SO_4$  solution. Fabrication process is completed by 50 nm Al deposition using thermal evaporator for source/drain contacts.

# **III. RESULTS AND DISCUSSION**

## A. Electrical characterization of ZnO TFTs

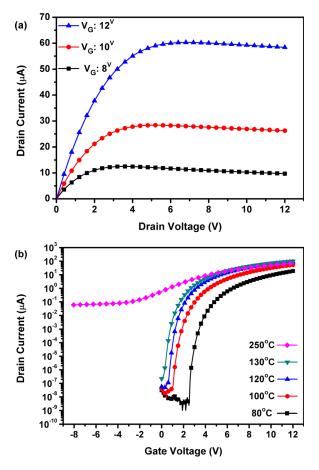

Electrical characteristics of ZnO TFTs are measured with a semiconductor parameter analyzer (Keithley 4200-SCS with 4200-CVU) and a DC probe station (Cascade PM-5).  $\rm I_D - V_{DS}$  characteristics of devices grown at 80  $^{\circ} \rm C$  are shown in Fig. 4(a). Results show that the devices exhibit n-channel enhancement mode MOSFET characteristics as expected.

Table II shows extracted threshold voltage values, subthreshold slopes,  $I_{on}/I_{off}$  ratios, and mobility values of TFTs fabricated on ZnO channel layers grown at different temperatures. Extrapolation method in the saturation region is implemented on measured  $\sqrt{I_D} - V_G$  characteristics of the devices. Subthreshold slopes are extracted

Fig. 4. (Color online) (a)  $I_D$ – $V_{DS}$  characteristics of devices grown at 80 °C, (b)  $I_D$ – $V_{DS}$  characteristics of devices having ZnO channel grown at 80, 100, 120, 130, and 250 °C with a channel length of 40  $\mu$ m and a channel width of 50  $\mu$ m.

TABLE II. Transistor characteristics with respect to growth temperature.

| Deposition temperature (°C) | Threshold voltage (V) | I <sub>on</sub> /I <sub>off</sub><br>ratio | Subthreshold slope (V/dec) | Mobility<br>(cm <sup>2</sup> /V s) |

|-----------------------------|-----------------------|--------------------------------------------|----------------------------|------------------------------------|

| 250                         | -0.7                  | $10^{3}$                                   | 3                          | 23                                 |

| 130                         | 1.58                  | $4.5 \times 10^{8}$                        | 0.165                      | 15.91                              |

| 120                         | 2.09                  | $1.8 \times 10^{9}$                        | 0.140                      | 14.9                               |

| 100                         | 2.8                   | $2 \times 10^{9}$                          | 0.170                      | 8.94                               |

| 80                          | 4.3                   | $7.8 \times 10^{9}$                        | 0.116                      | 3.96                               |

from  $log(I_D-V_G)$  characteristics of the devices using the formula of  $dV_G/dLog(I_D).$  Device mobility values were calculated using output  $\,I_D-V_D\,$  characteristics. Oxide capacitance is calculated using the equation

$$C_{ox} = \varepsilon_{ox}/t_{ox},$$

(1)

$$C_{ox} = \varepsilon_0.\varepsilon_r/t_{ox}, \qquad (2)$$

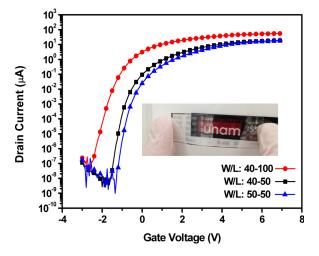

Fig. 5. (Color online)  $I_D$ – $V_{\rm GS}$  characteristics of devices having different channel length and width values fabricated on PET substrates.

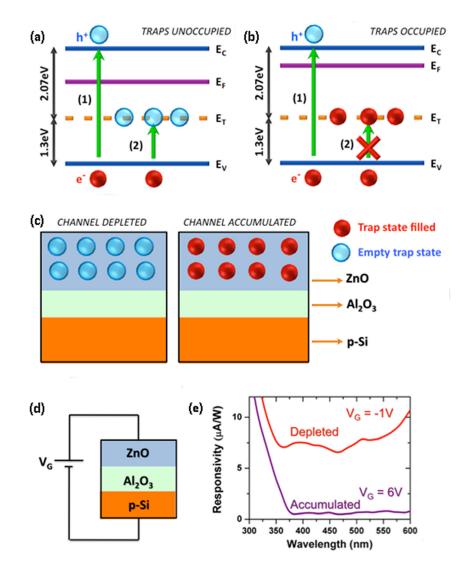

Fig. 6. (Color online) Trap related optical characteristics of ZnO deposited at  $80\,^{\circ}$ C. Energy band diagram depicting trap states (a) unoccupied and (b) occupied by an electron. Band-to-band (1) and valence band-to-trap state (2) absorption mechanisms are shown by arrows. When the traps are occupied, second transition is suppressed. (c) Illustration of the MOS gate sketch of TFT devices comprised of p-Si/Al<sub>2</sub>O<sub>3</sub>/ZnO. ALD-grown ZnO is the channel layer. (d) Applied gate bias voltage and measured spectral photoresponsivity at accumulated state ( $V_G = 6 \, V$ ) and depleted state ( $V_G = -1 \, V$ ).

where  $\varepsilon_r$  denotes dielectric constant of ALD deposited Al<sub>2</sub>O<sub>3</sub> (taken as 9 in calculations <sup>18,19</sup>).

Electrical characteristics exhibit similar trend with XPS results. As growth temperature increases, O/Zn ratio in the film decreases, which results in higher effective doping. 20–23 At low deposition temperature, O-H bonds passivate the defects and therefore reduce carrier concentration and increase  $I_{\rm on}/I_{\rm off}$  ratio. However, defects' detrimental effect on mobility is still present, which increases due to presence of hydrogen impurity scattering at low temperatures. It was proposed that oxygen vacancies and zinc interstitials are responsible for the n-type behavior of ZnO films due to the creation of shallow donor levels below the conduction band of ZnO. As a result, high O-H concentration means high O/Zn ratio, which results in less unintentional doping concentration. 13

Flexible ZnO TFT devices are fabricated using films grown at  $80\,^{\circ}$ C, since  $80\,^{\circ}$ C-growth results in the highest  $I_{on}/I_{off}$  ratios and the lowest subthreshold slopes.  $I_{D}$ – $V_{GS}$  characterization results showed that devices on different substrates (Si and PET) show similar electrical behavior. Flexible devices, which have a channel length of  $40\,\mu m$  and channel width of  $50\,\mu m$ , have  $I_{on}/I_{off}$  ratio on the order of  $10^8$ . Subthreshold slope of flexible TFTs with the same channel dimensions is found to be  $0.142\,V/dec$ , which is also similar to that of the device, built on Si substrate. Electron mobility and threshold voltage values are extracted as  $8.40\,cm^2/V$  s and  $-0.23\,V$ , respectively (see Fig. 5).

#### B. Optical characterization of ZnO TFTs

Crystal defects in ZnO create energy states in the forbidden band gap of ZnO.<sup>24</sup> Spectral photoluminescence (PL) characteristics obtained from 42-nm-thick ZnO layer deposited at 80 °C on double side polished quartz revealed that ZnO film has a broad PL spectrum centered around 600 nm (2.07 eV).<sup>8</sup> Through these defect states, ZnO can absorb photons with energy lower than its bandgap energy (3.37 eV). Such a sub-bandgap transition could occur through the excitation of an electron from valence band to trap state (transition 2 in Fig. 6) and from trap state to conduction band (not shown in Fig. 6). To excite electrons from valence band to trap state (transition 2), an unoccupied trap state is required.

To investigate sub-bandgap photosensing properties of ZnO based TFTs, devices are illuminated from the top (ZnO) side with a mechanically chopped (395 Hz) monochromatic light. The photogenerated current is measured using a lock-in amplifier. Visible light absorption of ZnO based TFTs can be actively controlled by external gate bias as shown in Fig. 6. When strong negative gate bias is applied, electrons are depleted from n-ZnO channel region. The number of unoccupied trap states and hence the probability of sub-band gap photon absorption will increase. On the other hand, as more positive gate bias is applied, electrons are accumulated to the channel layer, number of unoccupied traps and probability of sub-band gap absorption will decrease.

## IV. CONCLUSION

We present the effect of channel layer growth temperature on the electrical characteristics of bottom-gate ZnO TFTs. The effective carrier concentration and hence the electrical properties of TFTs are strongly influenced by ZnO deposition temperature. Functional TFTs on flexible substrates based on ALD-grown ZnO films are also demonstrated. Furthermore, we demonstrated the dynamic control of light absorption in ALD-grown ZnO TFTs. Electrical tuning of the optical response of ZnO based TFTs to visible light is experimentally verified and explained by the occupancy of deep level traps in ZnO films.

## **ACKNOWLEDGMENTS**

This work was supported by The Scientific and Technological Research Council of Turkey (TUBITAK) under Grant Nos. 109E044, 11A015, 112M004, 112E052, 112M482, and 113M815.

<sup>1</sup>D. Kim, H. Kang, J. M. Kim, and H. Kim, Appl. Surf. Sci. **257**, 7906 (2011).

<sup>2</sup>N. Huby, S. Ferrari, E. Guziewicz, M. Godlewski, and V. Osinniy, Appl. Phys. Lett. **92**, 023502 (2008).

<sup>3</sup>E. M. C. Fortunato, P. M. C. Barquinha, A. C. M. B. G. Pimentel, A. M. F. Gonçalves, A. J. S. Marques, L. M. N. Pereira, and R. F. P. Martins, Adv. Mater. 17, 590 (2005).

<sup>4</sup>E. Fortunato, P. Barquinha, A. Pimentel, A. Gonçalves, A. Marques, L. Pereira, and R. Martins, Thin Solid Films **487**, 205 (2005).

<sup>5</sup>R. L. Hoffman, B. J. Norris, and J. F. Wager, Appl. Phys. Lett. **82**, 733 (2003).

<sup>6</sup>Y. Kawamura, M. Horita, Y. Ishikawa, and Y. Uraoka, in *Proceedings of the 19th International Workshop on Active-Matrix Flatpanel Displays and Devices (AM-FPD)* (2012), pp. 179–182.

<sup>7</sup>P. F. Carcia, R. S. McLean, M. H. Reilly, and G. Nunes, Jr., Appl. Phys. Lett. **82**, 1117 (2003).

<sup>8</sup>L. E. Aygun, F. B. Oruc, F. B. Atar, and A. K. Okyay, IEEE Photonics J. 5, 2200707 (2013).

<sup>9</sup>A. Ohtomo and A. Tsukazaki, Semicond. Sci. Technol. **20**, S1 (2005).

<sup>10</sup>M. D. Barankin, E. Gonzalez II, A. M. Ladwig, and R. F. Hicks, Sol. Energy Mater. Sol. Cells 91, 924 (2007).

<sup>11</sup>J. B. Lee, H. J. Kim, S. G. Kim, C. S. Hwang, S. H. Hong, Y. H. Shin, and N. H. Lee, Thin Solid Films 435, 179 (2003).

<sup>12</sup>J. H. Lee, K. H. Ko, and B. O. Park, J. Cryst. Growth **247**, 119 (2003).

<sup>13</sup>S. Kwon *et al.*, Semicond. Sci. Technol. **24**, 035015 (2009).

<sup>14</sup>J. H. Kwon, J. H. Seo, S. Shin, and B. K. Ju, J. Phys. D: Appl. Phys. 42, 065105 (2009).

<sup>15</sup>E. M. C. Fortunato, P. M. C. Barquinha, A. C. M. B. G. Pimentel, A. M. F. Gonçalves, A. J. S. Marques, R. F. P. Martins, and L. M. N. Pereira, Appl. Phys. Lett. 85, 2541 (2004).

<sup>16</sup>S. Masuda, K. Kitamura, Y. Okumura, S. Miyatake, H. Tabata, and T. Kawai, J. Appl. Phys. 93, 1624 (2003).

<sup>17</sup>J. Siddiqui, E. Cagin, D. Chen, and J. D. Phillips, Appl. Phys. Lett. 88, 212903 (2006).

<sup>18</sup>J. Koo, J. Lee, S. Kim, Y. D. Kim, H. Jeon, D. S. Kim, and Y. Kim, J. Korean Phys. Soc. 47, 501 (2005).

<sup>19</sup>M. J. Biercuk, D. J. Monsma, C. M. Marcus, J. S. Becker, and R. G. Gordon, Appl. Phys. Lett. 83, 2405 (2003).

<sup>20</sup>E. Guziewicz *et al.*, Microelectron. J. **40**, 293 (2009).

<sup>21</sup>S. J. Pearton, D. P. Norton, K. Ip, Y. W. Heo, and T. Steiner, Superlattices Microstruct. 34, 3 (2003).

<sup>22</sup>Ü. Özgür et al., J. Appl. Phys. 98, 041301 (2005).

<sup>23</sup>C. Klingshirn, Phys. Status Solidi B **244**, 3027 (2007).

<sup>24</sup>E. Guziewicz *et al.*, Semicond. Sci. Technol. **27**, 074011 (2012).